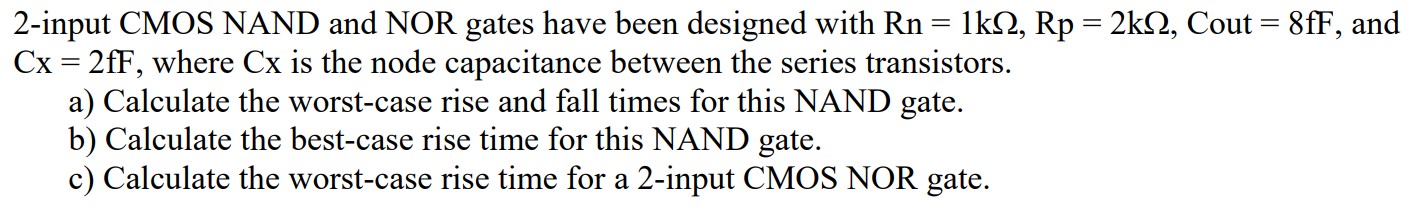

2-input CMOS NAND and NOR gates have been designed with Rn = 1kohm, Rp = 2kohm, Cout = 8fF, and Cx = 2fF, where Cx is the node capacitance between the series transistors. a) Calculate the worst-case rise and fall times for this NAND gate. b) Calculate the best-case rise time for this NAND gate. c) Calculate the worst-case rise time for a 2-input CMOS NOR gate.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers