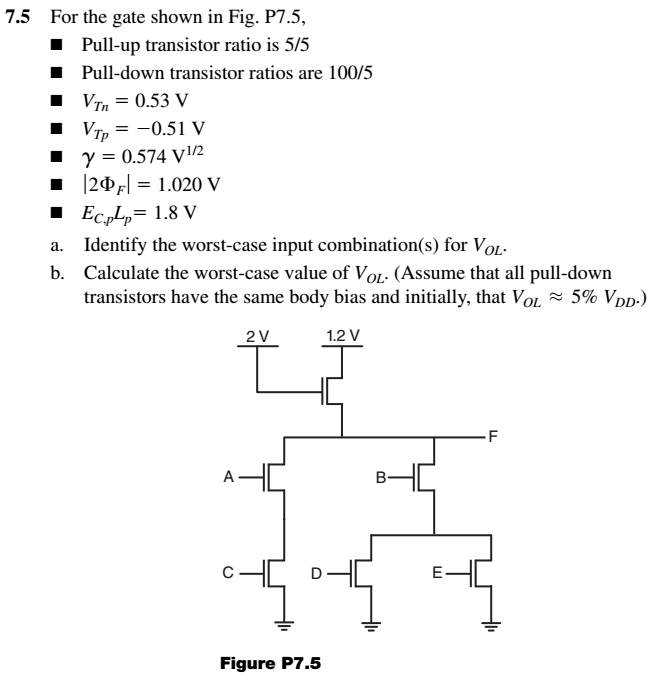

7.5 For the gate shown in Fig. P7.5, Pull-up transistor ratio is 5/5 Pull-down transistor ratios are 100/5 VTn = 0.53 V VTp = −0.51 V γ = 0.574 V1 /2 |2ΦF| = 1.020 V EC,pLp = 1.8 V a. Identify the worst-case input combination(s) for VOL. b. Calculate the worst-case value of VOL. (Assume that all pull-down transistors have the same body bias and initially, that VOL ≈ 5% VDD. ) Figure P7.5