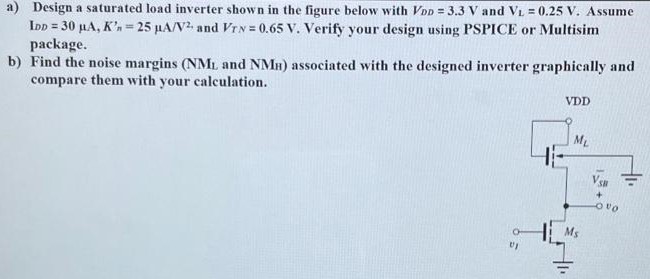

a) Design a saturated load inverter shown in the figure below with VDD = 3.3 V and VL = 0.25 V . Assume IDD = 30 μA, Kn' = 25 μA/V2, and VTN = 0.65 V. Verify your design using PSPICE or Multisim package. b) Find the noise margins (NML and NMH) associated with the designed inverter graphically and compare them with your calculation.