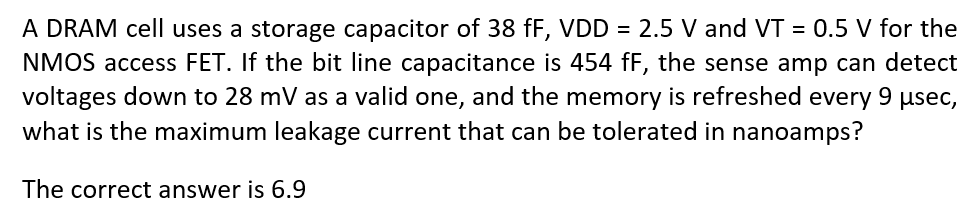

A DRAM cell uses a storage capacitor of 38 fF, VDD = 2.5 V and VT = 0.5 V for the NMOS access FET. If the bit line capacitance is 454 fF, the sense amp can detect voltages down to 28 mV as a valid one, and the memory is refreshed every 9 μsec, what is the maximum leakage current that can be tolerated in nanoamps? The correct answer is 6.9

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers