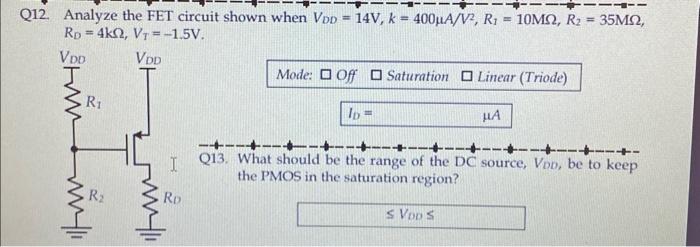

Analyze the FET circuit shown when VDD = 14V, k = 400 uA/V^2, R1 = 10Mohm, R2 = 35Mohm, RD = 4kohm, VT = -1.5 V. What should be the range of the DC source, VDD, be to keep the PMOS in the saturation region?

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers