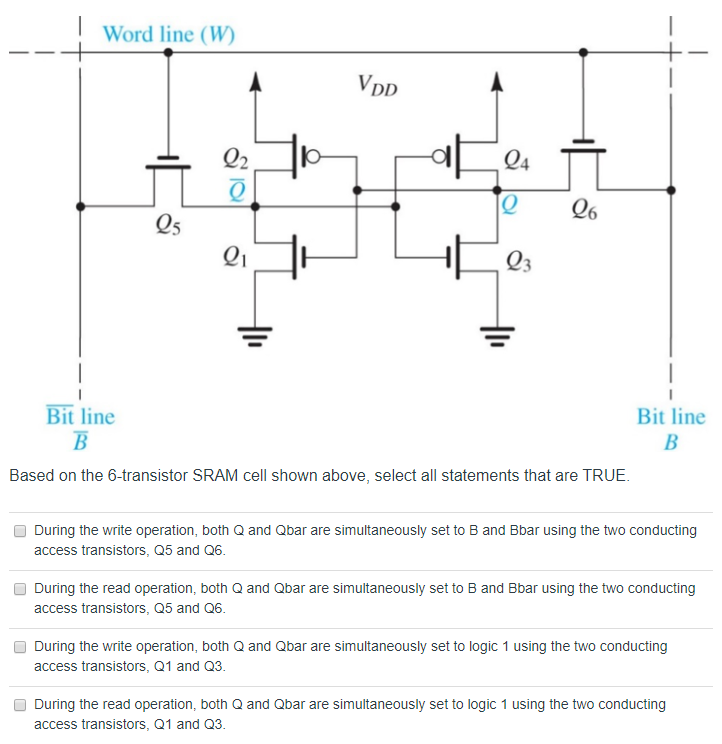

Based on the 6-transistor SRAM cell shown above, select all statements that are TRUE. During the write operation, both Q and Qbar are simultaneously set to B and Bbar using the two conducting access transistors, Q5 and Q6. During the read operation, both Q and Qbar are simultaneously set to B and Bbar using the two conducting access transistors, Q5 and Q6. During the write operation, both Q and Qbar are simultaneously set to logic 1 using the two conducting access transistors, Q1 and Q3. During the read operation, both Q and Qbar are simultaneously set to logic 1 using the two conducting access transistors, Q1 and Q3.