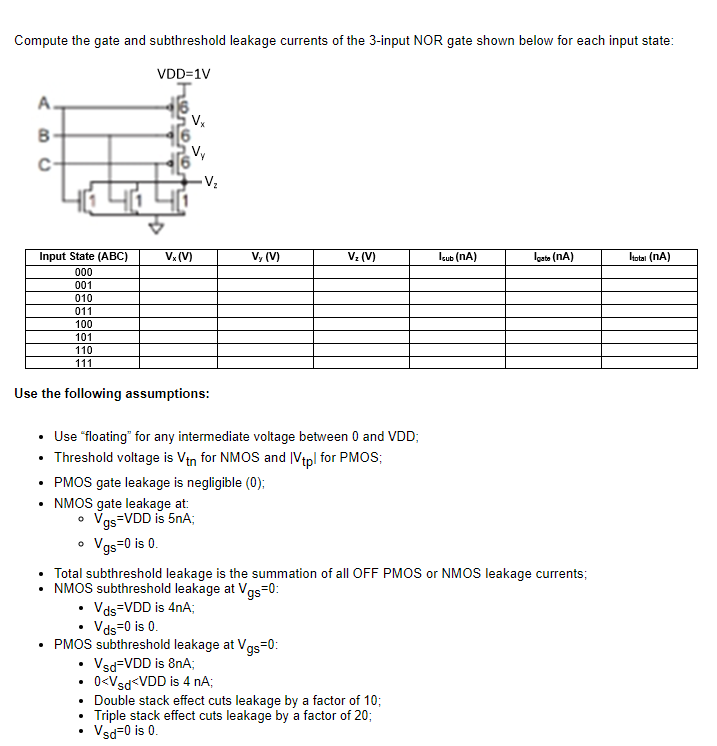

Compute the gate and subthreshold leakage currents of the 3 -input NOR gate shown below for each input state: Use the following assumptions: Use "Floating" for any intermediate voltage between 0 and VDD; Threshold voltage is Vtn for NMOS and |Vtp| for PMOS. PMOS gate leakage is negligible (0); NMOS gate leakage at: Vgs=VDD is 5nA. Vgs =0 is 0 Total subthreshold leakage is the summation of all OFF PMOS or NMOS leakage currents; NMOS subthreshold leakage at Vgs=0: Vds=VDD is 4nA; Vds=0 is 0. PMOS subthreshold leakage at Vgs=0: Vsd =VDD is 8nA. 0

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers