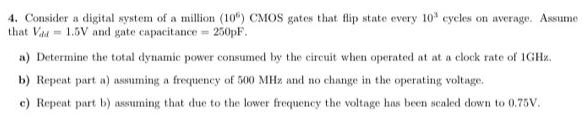

Consider a digital system of a million (10^6) CMOS gates that flip state every 10^3 cycles on average. Assume that Vdd = 1.5 V and gate capacitance = 250 pF. a) Determine the total dynamic power consumed by the circuit when operated at at a clock rate of 1GHz. b) Repeat part a) assuming a frequency of 500 MHz and no change in the operating voltage. c) Repeat part b) assuming that due to the lower frequency the voltage has been sealed down to 0.75 V.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers