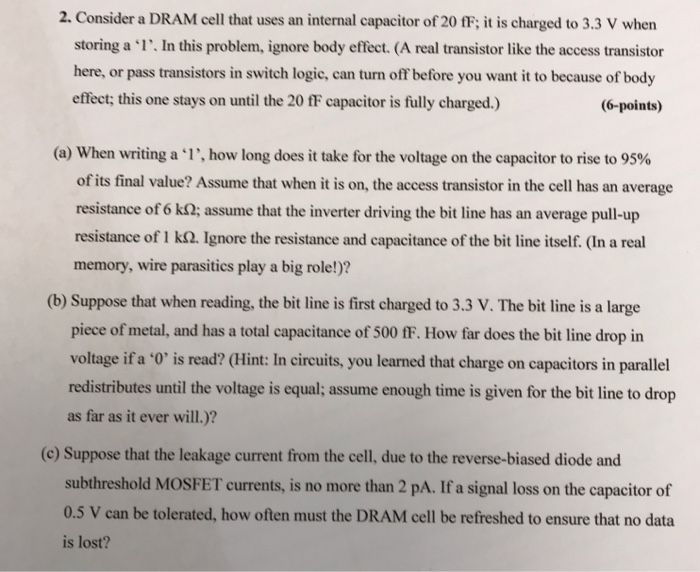

Consider a DRAM cell that uses an internal capacitor of 20 fF; it is charged to 3.3 V when storing a ' 1 '. In this problem, ignore body effect. (A real transistor like the access transistor here, or pass transistors in switch logic, can turn off before you want it to because of body effect; this one stays on until the 20 fF capacitor is fully charged. ) (6-points) (a) When writing a ' 1 ', how long does it take for the voltage on the capacitor to rise to 95% of its final value? Assume that when it is on, the access transistor in the cell has an average resistance of 6 kΩ; assume that the inverter driving the bit line has an average pull-up resistance of 1 kΩ. Ignore the resistance and capacitance of the bit line itself. (In a real memory, wire parasitics play a big role!)? (b) Suppose that when reading, the bit line is first charged to 3.3 V. The bit line is a large piece of metal, and has a total capacitance of 500 fF. How far does the bit line drop in voltage if a ' 0 ' is read? (Hint: In circuits, you learned that charge on capacitors in parallel redistributes until the voltage is equal; assume enough time is given for the bit line to drop as far as it ever will. )? (c) Suppose that the leakage current from the cell, due to the reverse-biased diode and subthreshold MOSFET currents, is no more than 2 pA. If a signal loss on the capacitor of 0.5 V can be tolerated, how often must the DRAM cell be refreshed to ensure that no data is lost?