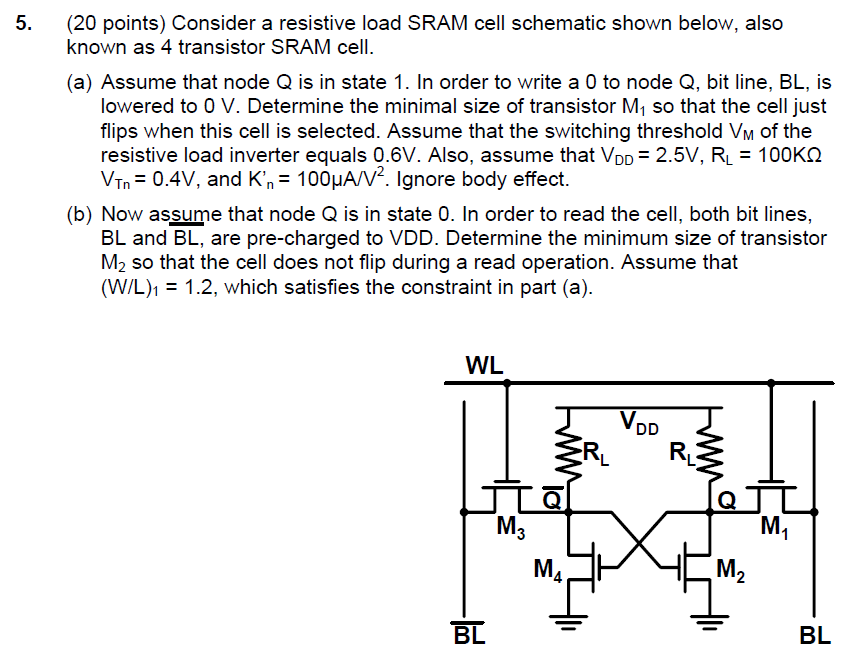

Consider a resistive load SRAM cell schematic shown below, also known as 4 transistor SRAM cell. (a) Assume that node Q is in state 1 . In order to write a 0 to node Q, bit line, BL, is lowered to 0 V. Determine the minimal size of transistor M1 so that the cell just flips when this cell is selected. Assume that the switching threshold VM of the resistive load inverter equals 0.6 V. Also, assume that VDD = 2.5 V, RL = 100 KΩ VTn = 0.4 V, and Kn = 100 μA/V2. Ignore body effect. (b) Now assume that node Q is in state 0 . In order to read the cell, both bit lines, BL and BL, are pre-charged to VDD. Determine the minimum size of transistor M2 so that the cell does not flip during a read operation. Assume that (W/L)1 = 1.2, which satisfies the constraint in part (a).