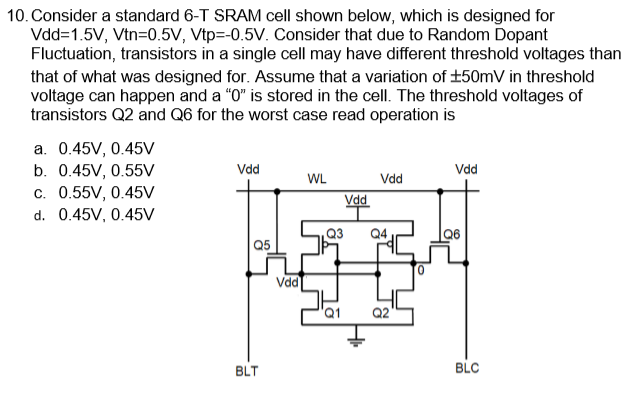

Consider a standard 6-T SRAM cell shown below, which is designed for Vdd = 1.5 V, V tn = 0.5 V, Vtp = −0.5 V. Consider that due to Random Dopant Fluctuation, transistors in a single cell may have different threshold voltages than that of what was designed for. Assume that a variation of ±50 mV in threshold voltage can happen and a "0" is stored in the cell. The threshold voltages of transistors Q2 and Q6 for the worst case read operation is a. 0.45 V, 0.45 V b. 0.45 V, 0.55 V c. 0.55 V, 0.45 V d. 0.45 V, 0.45 V