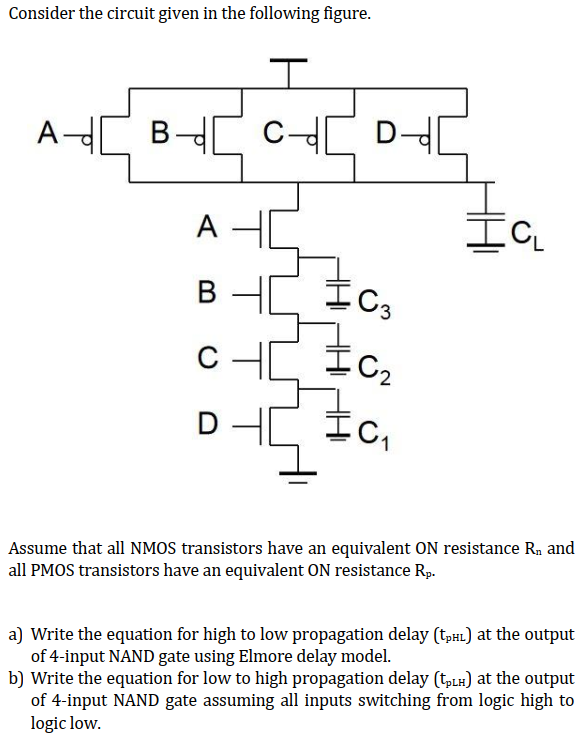

Consider the circuit given in the following figure. Assume that all NMOS transistors have an equivalent ON resistance Rn and all PMOS transistors have an equivalent ON resistance Rp. a) Write the equation for high to low propagation delay (tpHL) at the output of 4-input NAND gate using Elmore delay model. b) Write the equation for low to high propagation delay (tpLH) at the output of 4-input NAND gate assuming all inputs switching from logic high to logic low.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers