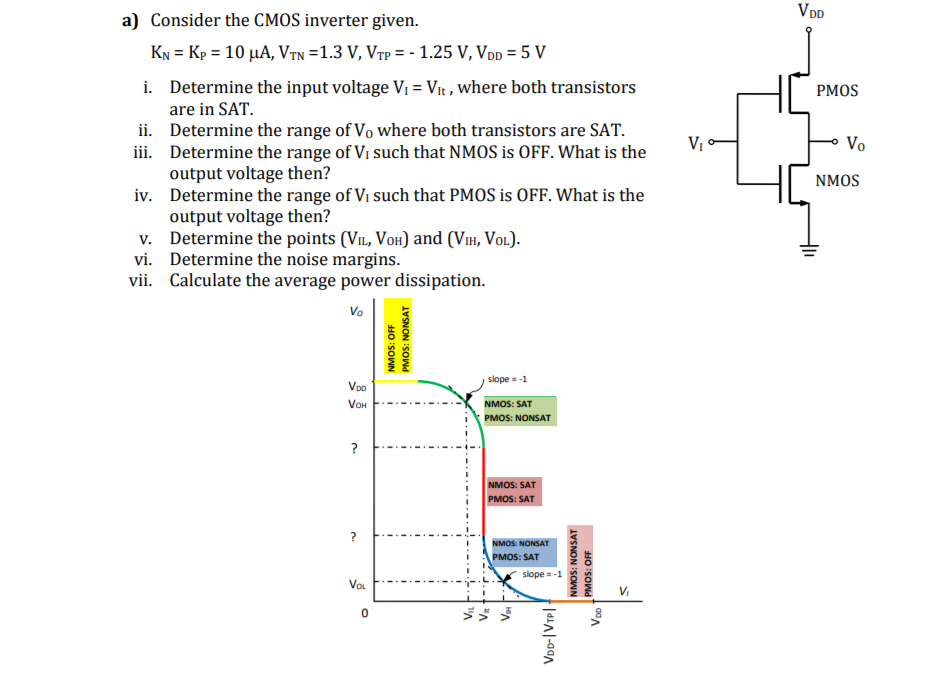

Consider the CMOS inverter given. KN = KP = 10 uA/V2, VTN = 1.3 V, VTP = -1.25 V, VDD = 5 V i. Determine the input voltage VI = VIt, where both transistors PMOS are in SAT. ii. Determine the range of VO where both transistors are SAT. iii. Determine the range of VI such that NMOS is OFF. What is the output voltage then? iv. Determine the range of VI such that PMOS is OFF. What is the output voltage then? v. Determine the points (VIL, VOH) and (VIH, VOL,) vi. Determine the noise margins vii. Calculate the average power dissipation.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers