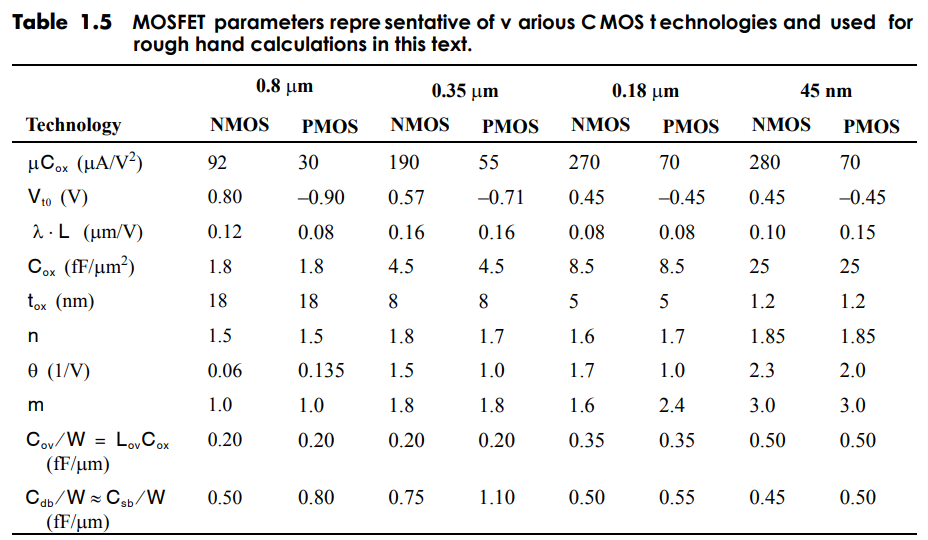

Consider the current mirror depicted in Fig. P3.6 where Iin = 100 µA, R = 2 kΩ, and each transistor has W/L = 10 µm/0.4 µm. Given the 0.35-μm CMOS device parameters in Table 1.5, what drain voltage at Q2 will ensure that Iin is precisely equal to Iout?

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers