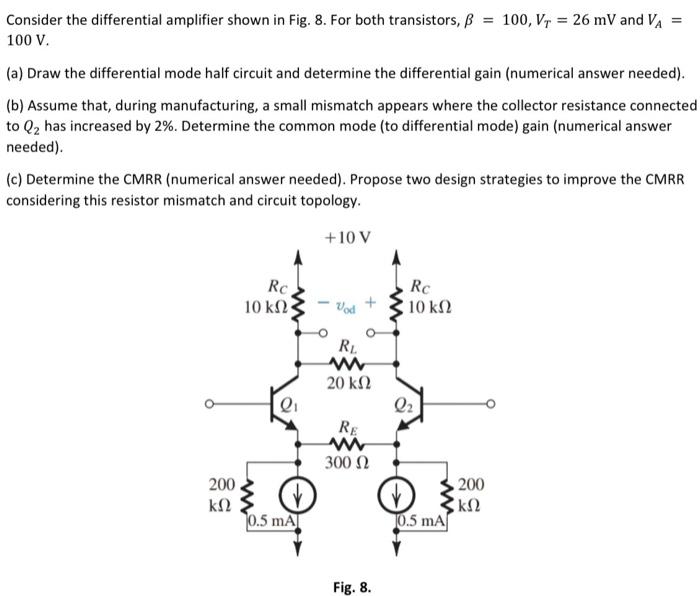

Consider the differential amplifier shown in Fig. 8. For both transistors, β = 100, VT = 26 mV and VA = 100 V. (a) Draw the differential mode half circuit and determine the differential gain (numerical answer needed). (b) Assume that, during manufacturing, a small mismatch appears where the collector resistance connected to Q2 has increased by 2%. Determine the common mode (to differential mode) gain (numerical answer needed). (c) Determine the CMRR (numerical answer needed). Propose two design strategies to improve the CMRR considering this resistor mismatch and circuit topology. Fig. 8.