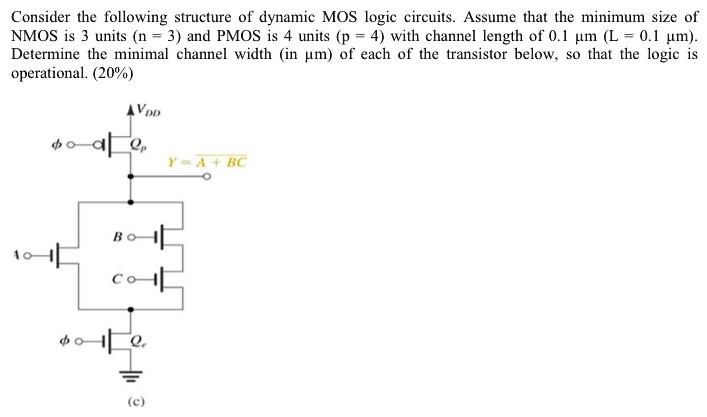

Consider the following structure of dynamic MOS logic circuits. Assume that the minimum size of NMOS is 3 units (n = 3) and PMOS is 4 units (p = 4) with channel length of 0.1 μm (L = 0.1 μm). Determine the minimal channel width (in μm ) of each of the transistor below, so that the logic is operational. (20%) (c)