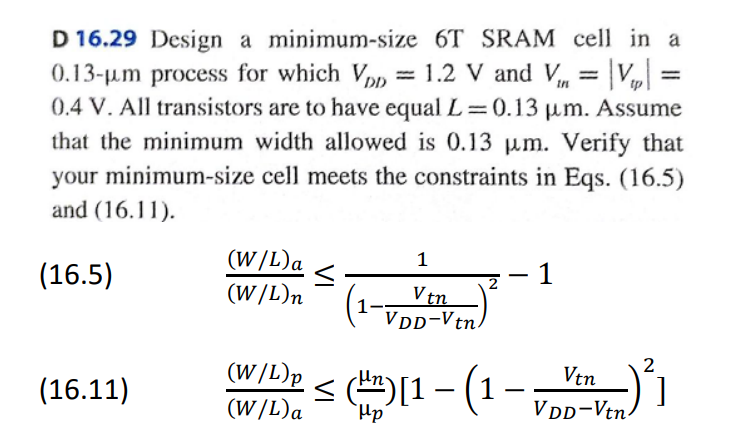

D 16.29 Design a minimum-size 6 T SRAM cell in a 0.13−μm process for which VDD = 1.2 V and Vtn = |Vt| = 0.4 V. All transistors are to have equal L = 0.13 μm. Assume that the minimum width allowed is 0.13 μm. Verify that your minimum-size cell meets the constraints in Eqs. (16.5) and (16.11).