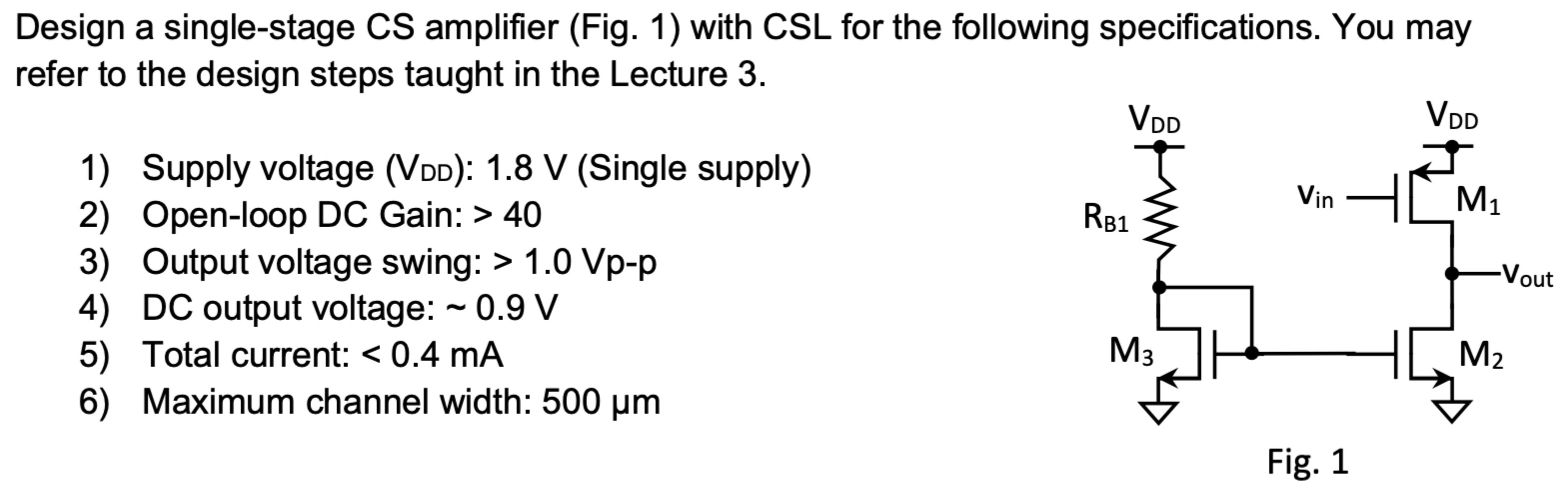

Design a single-stage CS amplifier (Fig. 1) with CSL for the following specifications. You may refer to the design steps taught in the Lecture 3. Supply voltage (VDD): 1.8 V (Single supply) Open-loop DC Gain: > 40 Output voltage swing: > 1.0 Vp−p DC output voltage: ∼0.9 V Total current: < 0.4 mA Maximum channel width: 500 μm Fig. 1