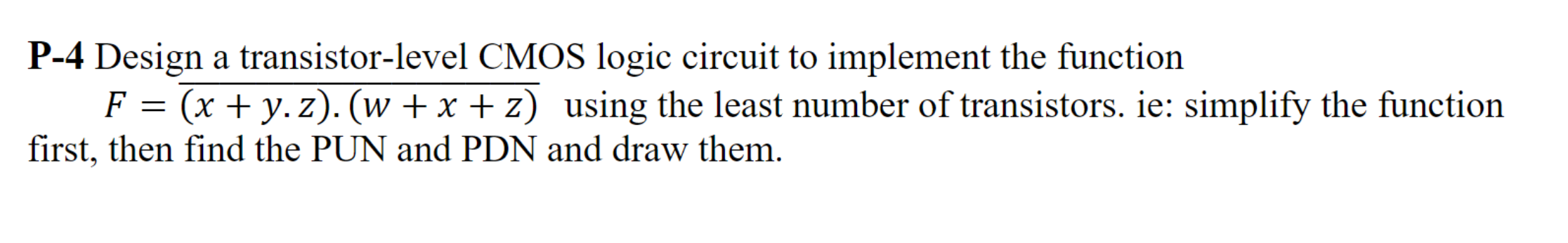

Design a transistor-level CMOS logic circuit to implement the function F = (x + y ⋅ z). (w + x + z) bar using the least number of transistors. ie: simplify the function first, then find the PUN and PDN and draw them.

According to the property of CMOS logic circuits, if complement is implemented in pull-down network then the output obtained is Boolean function F. Use following steps to implement given boolean function in CMOS technology.

Step (1): Since logic function F is given, we need first complement F to get .

Step (2): Simplify to implement PDN and PUN with minimum number of transistors.

Step (3): Implement simplified in PDN and dual of

in PUN.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers