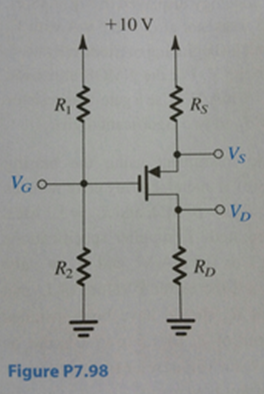

Design the circuit in Fig. P7.98 so that the transistor operates in saturation with VD biased 1 V from the edge of the triode region, with ID = 1 mA and VD = 3 V, for each of the following two devices (use a 10-uA current in the voltage divider): (a) |Vt| = 1 V and kp'W/L = 0.5 mA/V2 (b) |Vt| = 2 V and kp'W/L = 1.25 mA/V2 Figure P7.98 For each case, specify the values of VG, VD, VS, R1, R2, RS, and RD. Figure P7.98

D 7.98 Design the circuit in Fig. P7.98 so that the transistor operates in saturation with VD biased 1 V from the edge of the triode region, with ID = 1 mA and VD = 3 V, for each of the following two devices (use a 10-μA current in the voltage divider): (a) |Vt| = 1 V and kp'W/L = 0.5 mA/V2 (b) |Vt| = 2 V and kp'W/L = 1.25 mA/V2 For each case, specify the values of VG, VD, VS , R1, R2, RS , and RD.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers