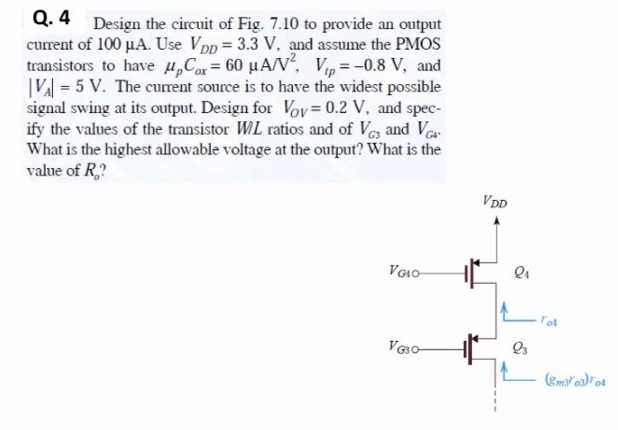

Design the circuit of Fig. 7.10 to provide an output current of 100 uA. Use VDD = 3.3 V, and assume the PMOS transistors to have upCox = 60 uA/V^2, Vtp = -0.8 V, and | VA| = 5 V. The current source is to have the widest possible signal swing at its output. Design for Vov = 0.2 V, and specify the values of the transistor W/L ratios and of VG3 and VG4. What is the highest allowable voltage at the output? What is the value of Ro?

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers