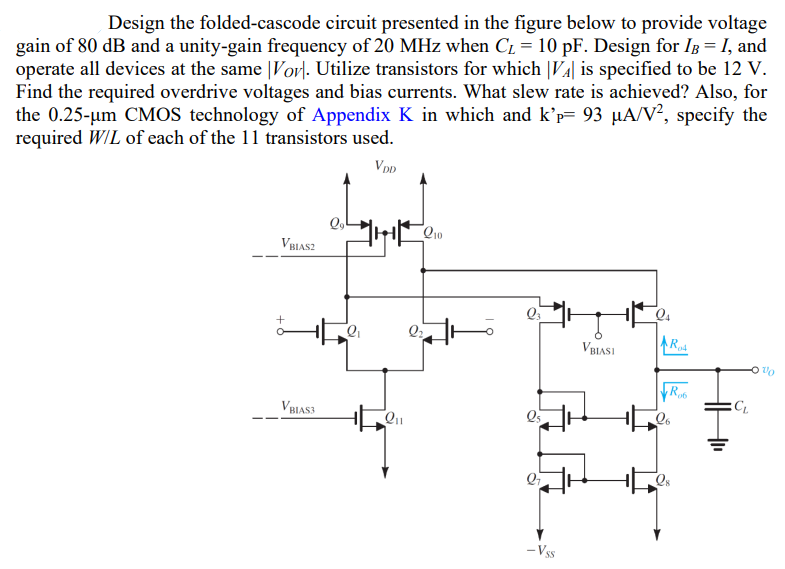

Design the folded-cascode circuit presented in the figure below to provide voltage gain of 80 dB and a unity-gain frequency of 20 MHz when CL = 10 pF. Design for IB = I, and operate all devices at the same |VOV|. Utilize transistors for which |VA| is specified to be 12 V. Find the required overdrive voltages and bias currents. What slew rate is achieved? Also, for the 0.25−μm CMOS technology of Appendix K in which and kp = 93 μA/V2, specify the required W/L of each of the 11 transistors used.