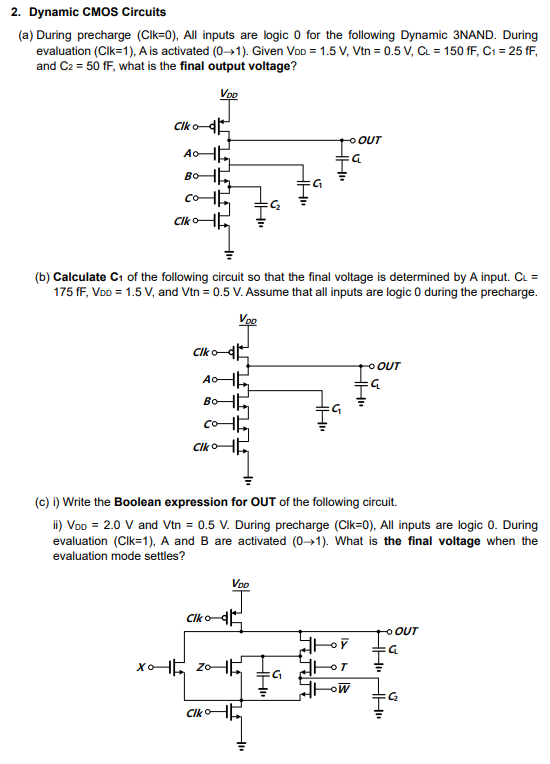

Dynamic CMOS Circuits (a) During precharge (Clk=0), All inputs are logic 0 for the following Dynamic 3NAND. During evaluation (Clk=1), A is activated (0 → 1). Given VDD = 1.5 V, Vtn = 0.5 V, CL = 150 fF, C1 = 25 fF, and C2 = 50 fF, what is the final output voltage? (b) Calculate C1 of the following circuit so that the final voltage is determined by A input. CL = 175 fF, VDD = 1.5 V, and Vtn = 0.5 V. Assume that all inputs are logic 0 during the precharge. (c) i) Write the Boolean expression for OUT of the following circuit. ii) VDD = 2.0 V and Vtn = 0.5 V. During precharge (Clk = 0), All inputs are logic 0. During evaluation (C∣k = 1), A and B are activated (0 → 1). What is the final voltage when the evaluation mode settles?