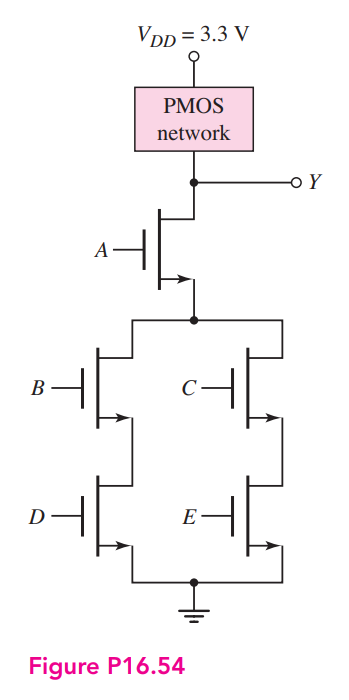

Figure P16.54 is a classic CMOS logic gate. (a) What is the logic function performed by the circuit? (b) Design the PMOS network. (c) Determine the transistor W/L ratios to provide symmetrical switching times at twice the switching speed as the basic CMOS inverter with (W/L)n = 2 and (W/L)p = 4.

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers