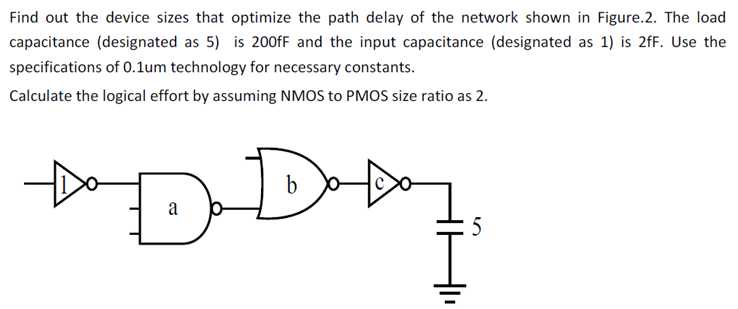

Find out the device sizes that optimize the path delay of the network shown in Figure. 2. The load capacitance (designated as 5) is 200 fF and the input capacitance (designated as 1) is 2 fF. Use the specifications of 0.1 um technology for necessary constants. Calculate the logical effort by assuming NMOS to PMOS size ratio as 2.