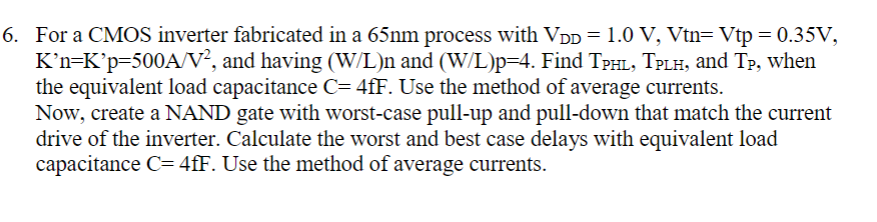

For a CMOS inverter fabricated in a 65nm process with VDD = 1.0 V, Vtn = Vtp = 0.35 V, K′n = K′p = 500 A/V2, and having (W/L)n and (W/L)p = 4. Find TPHL, TPLH, and TP, when the equivalent load capacitance C = 4 fF. Use the method of average currents. Now, create a NAND gate with worst-case pull-up and pull-down that match the current drive of the inverter. Calculate the worst and best case delays with equivalent load capacitance C = 4 fF. Use the method of average currents.