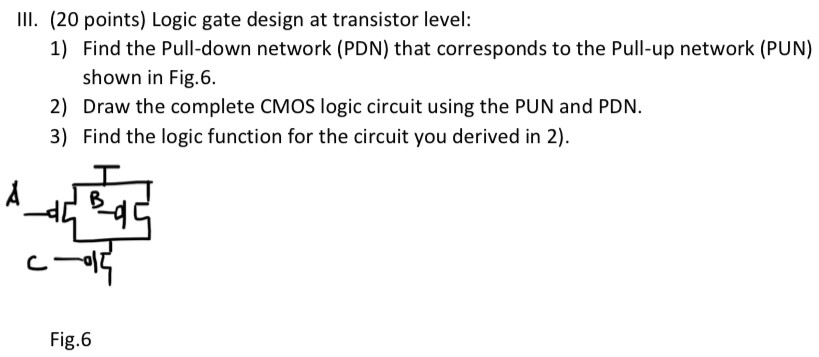

III. (20 points) Logic gate design at transistor level:Find the Pull-down network (PDN) that corresponds to the Pull-up network (PUN) shown in Fig. 6. Draw the complete CMOS logic circuit using the PUN and PDN. 3) Find the logic function for the circuit you derived in 2). Fig. 6