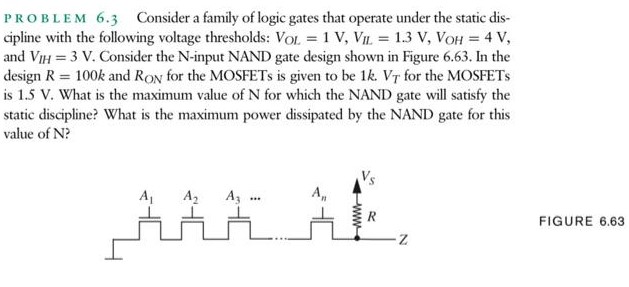

P R O B LEM 6.3 Consider a family of logic gates that operate under the static discipline with the following voltage thresholds: VOL = 1 V, VIL = 1.3 V, VOH = 4 V, and VIH = 3 V. Consider the N-input NAND gate design shown in Figure 6.63 . In the design R = 100 k and RON for the MOSFETs is given to be 1 k. VT for the MOSFETs is 1.5 V. What is the maximum value of N for which the NAND gate will satisfy the static discipline? What is the maximum power dissipated by the NAND gate for this value of N ? FIGURE 6.63