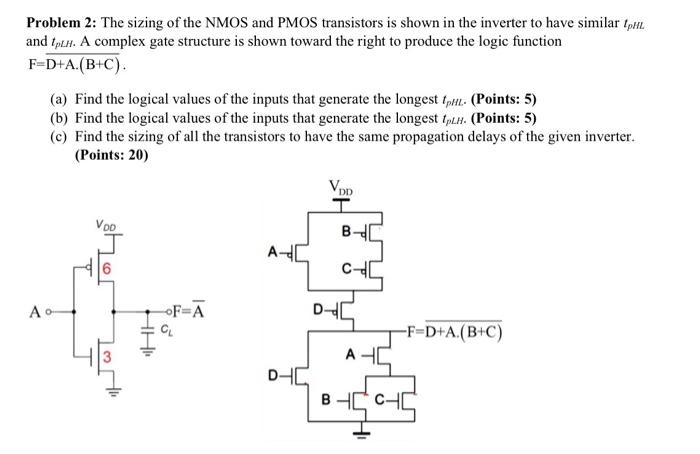

Problem 2: The sizing of the NMOS and PMOS transistors is shown in the inverter to have similar tpHL and tpLH. A complex gate structure is shown toward the right to produce the logic function F=D+A.(B+C) (a) Find the logical values of the inputs that generate the longest tpHL. (Points: 5) (b) Find the logical values of the inputs that generate the longest tpLH. (Points: 5) (c) Find the sizing of all the transistors to have the same propagation delays of the given inverter. (Points: 20)

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers