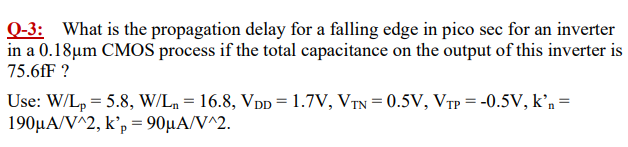

Q-3: What is the propagation delay for a falling edge in pico sec for an inverter in a 0.18 μm CMOS process if the total capacitance on the output of this inverter is 75.6 fF? Use: W/Lp = 5.8, W/Ln = 16.8, VDD = 1.7 V, VTN = 0.5 V, VTP = −0.5 V, kn = 190 μA/V∧2, kp′ = 90 μA/V^2.