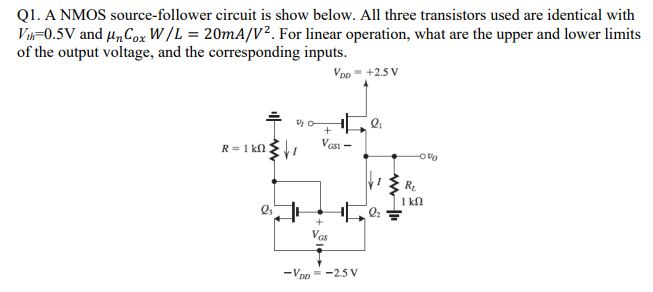

Q1. A NMOS source-follower circuit is show below. All three transistors used are identical with Vth = 0.5 V and μnCoxW/L = 20 mA/V2. For linear operation, what are the upper and lower limits of the output voltage, and the corresponding inputs. Calculate the average propagation delay of CMOS symmetric inverter shown in the figure below for C = 0.3 pF. Given KN′ = 100 μAV2 and VTN = 0.6 V. 1.2 ns 4.8 ns 3.6 ns 2.4 ns