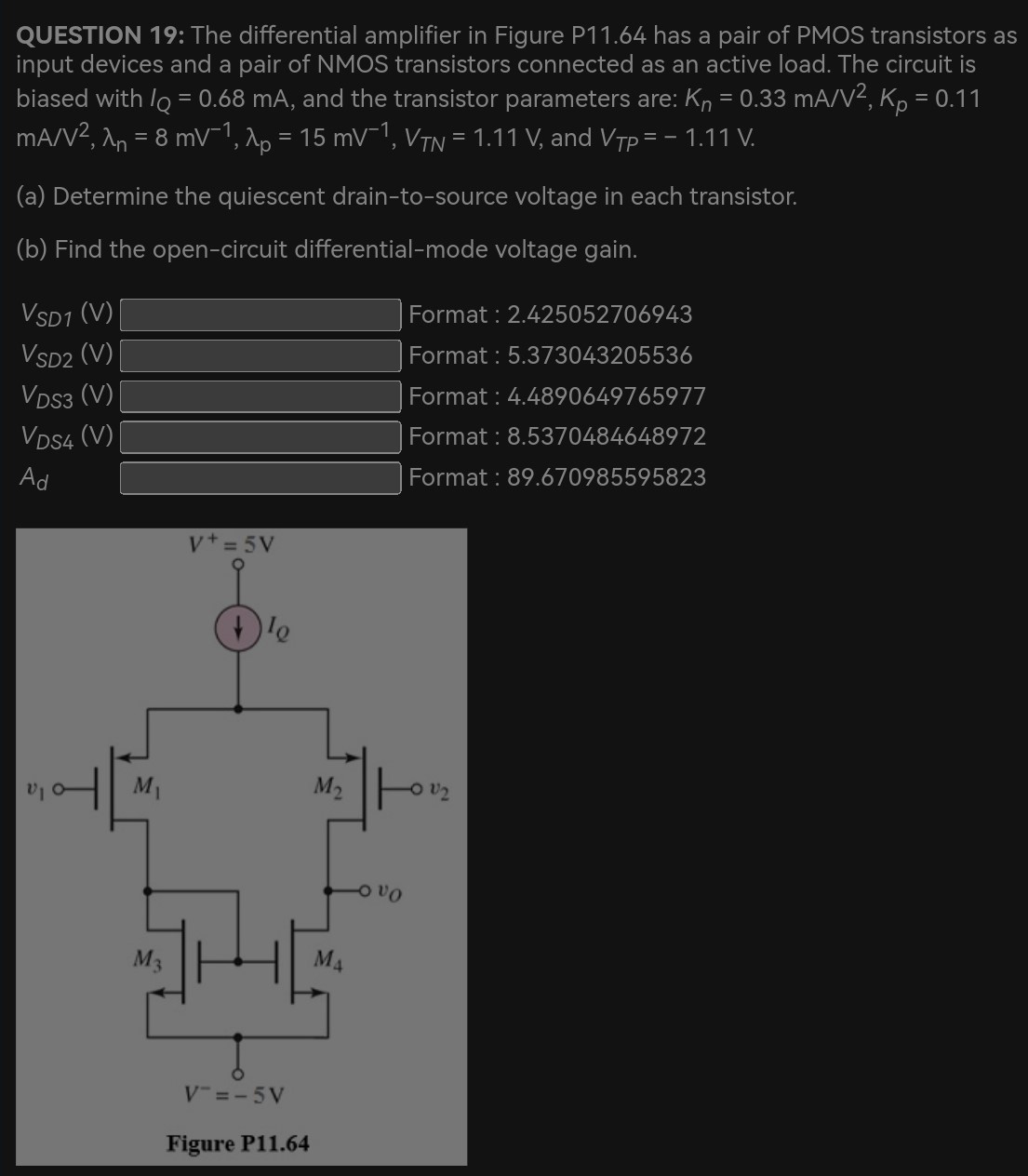

QUESTION 19: The differential amplifier in Figure P11.64 has a pair of PMOS transistors as input devices and a pair of NMOS transistors connected as an active load. The circuit is biased with IQ = 0.68 mA, and the transistor parameters are: Kn = 0.33 mA/V2, Kp = 0.11 mA/V2, λn = 8 mV−1, λp = 15 mV−1, VTN = 1.11 V, and VTP = −1.11 V. (a) Determine the quiescent drain-to-source voltage in each transistor. (b) Find the open-circuit differential-mode voltage gain. VSD1(V) Format : 2.425052706943 VSD2(V) Format : 5.373043205536 VDS3(V) Format : 4.4890649765977 VDS4(V) Format: 8.5370484648972 Ad Format : 89.670985595823 Figure P11.64