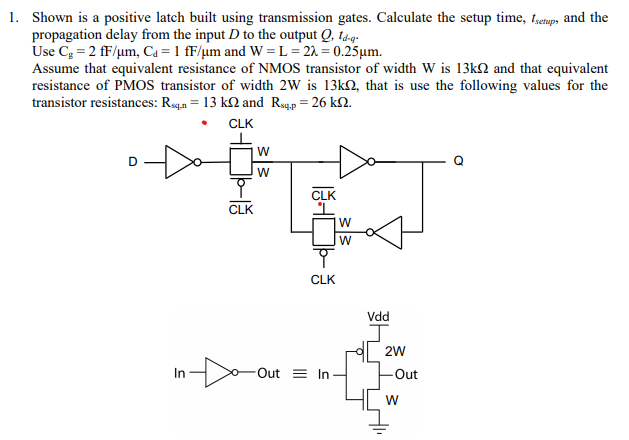

Shown is a positive latch built using transmission gates. Calculate the setup time, tsetup , and the propagation delay from the input D to the output Q, td−q. Use Cg = 2 fF/μm, Cd = 1 fF/μm and W = L = 2λ = 0.25 μm. Assume that equivalent resistance of NMOS transistor of width W is 13 kΩ and that equivalent resistance of PMOS transistor of width 2 W is 13 kΩ, that is use the following values for the transistor resistances: Rsq, n = 13 kΩ and Rsq, p = 26 kΩ.