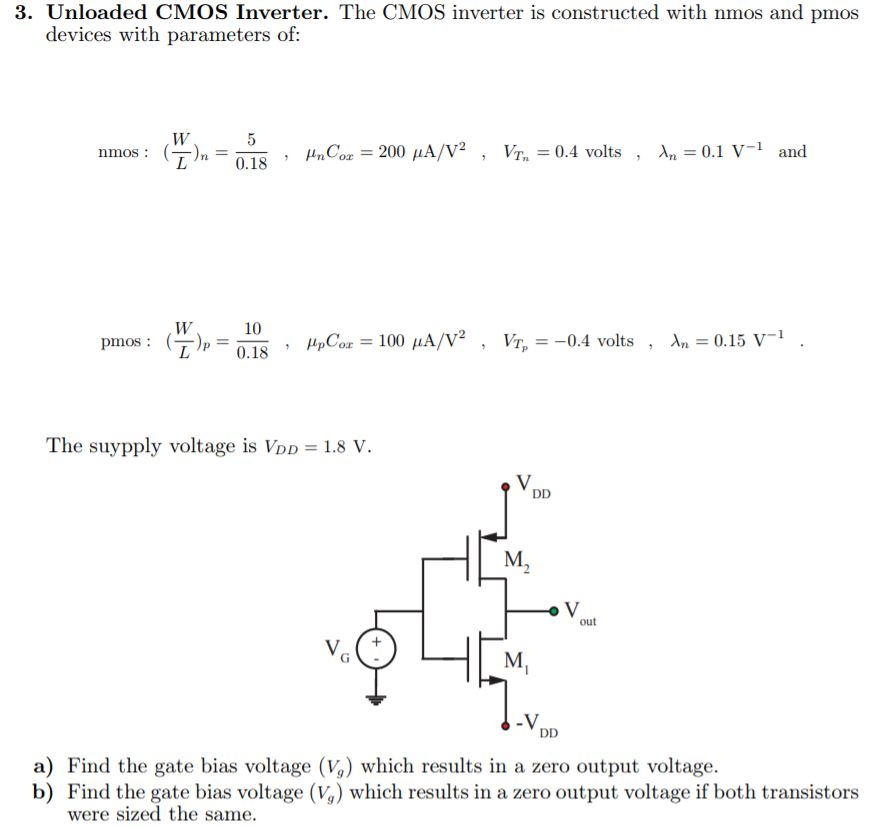

Unloaded CMOS Inverter. The CMOS inverter is constructed with nmos and pmos devices with parameters of: nmos:(W/L)n = 50.18, μnCox = 200 μA/V2, VTn = 0.4 volts, λn = 0.1 V−1 and pmos:(W/L)p = 100.18, μpCox = 100 μA/V2, VTp = −0.4 volts , λn = 0.15 V−1. The suypply voltage is VDD = 1.8 V. a) Find the gate bias voltage (Vg) which results in a zero output voltage. b) Find the gate bias voltage (Vg) which results in a zero output voltage if both transistors were sized the same.