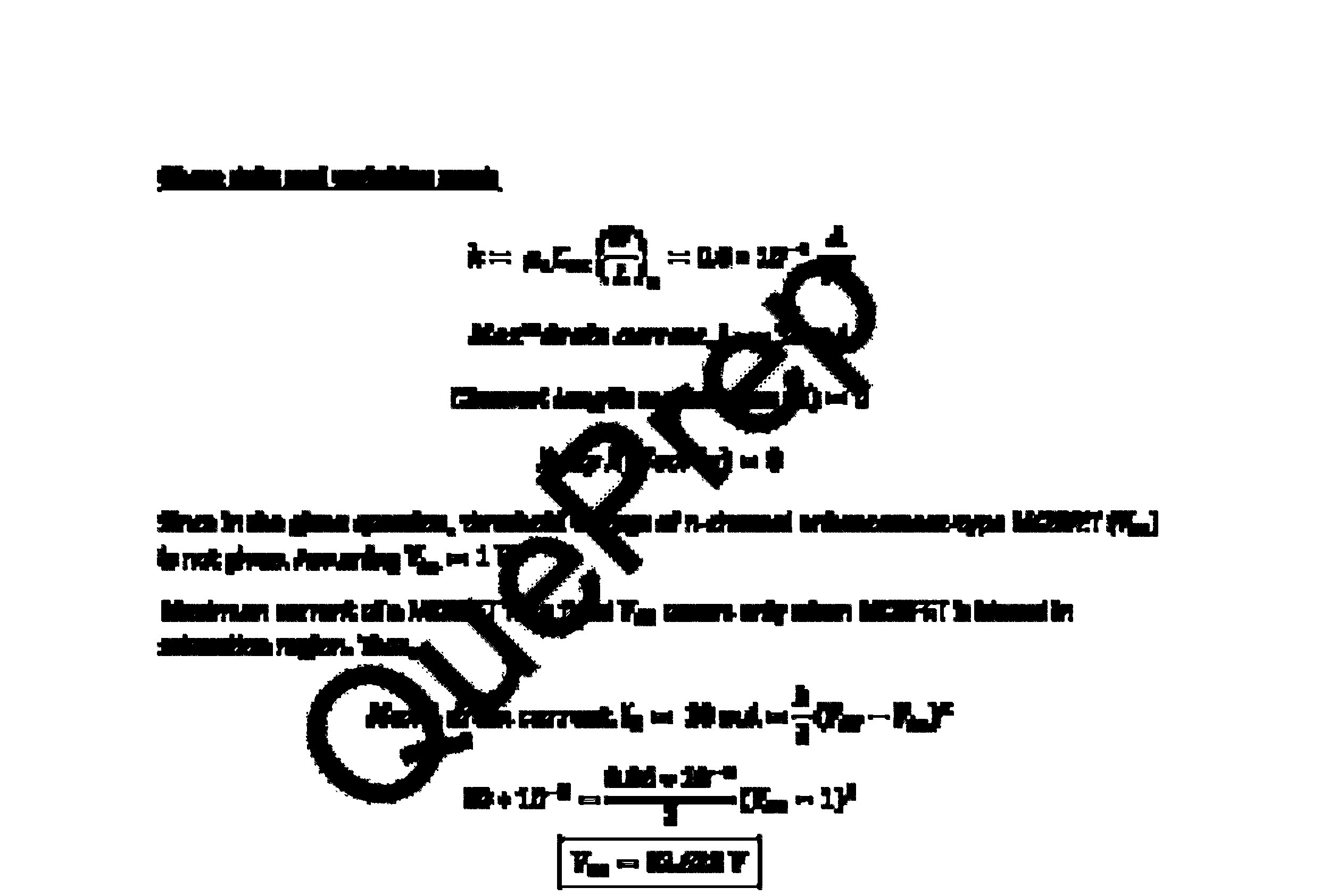

What will be the final output voltage in volts for a dynamic 4-input NAND gate if the top 3 NMOS FETs have a logic "1" on their inputs and the bottom NMOS FET has a logic "0" on it's input. Assume the total capacitance on the output is 89fF, and there is 6fF on each of the nodes between the series NMOS FETs. Neglect leakage. Use: VDD = 2.5V, VTN = 0.4V, VTP = -0.6V, k'n = 150uA/V^2, k'p = 60uA/V^2

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers