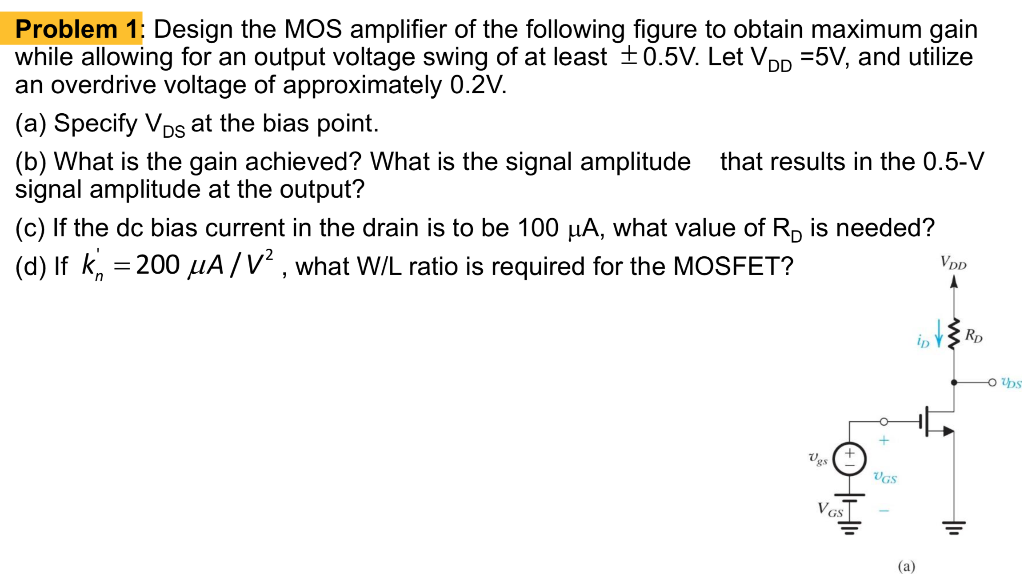

Design the MOS amplifier of Fig. 7.4(a) to obtain maximum gain while allowing for an output voltage swing of at least ±0.5V. Let VDD = 5V and utilize an overdrive voltage of approximately 0.2V a)Specify the VDS at the bias point b) What is the gain achieved? What is the signal amplitude vgs that results in the 0.5-V signal amplitude at the output? c)If the dc bias current in the drain is to be 100 μA what value of RD is needed? d) If k'n = 200 μA/V^2 , what W/L ratio is required for the MOSFET?

You'll get a detailed, step-by-step and expert verified solution.

Work With Experts to Reach at Correct Answers

Work With Experts to Reach at Correct Answers